Facultad de Ingeniería Universidad de Deusto

**Ingeniaritza Fakultatea** Deustuko Unibertsitatea

# Grado en Ingeniería en Electrónica Industrial y Automática Industria Elektronikako eta Automatikako Ingeniaritzako Gradua

# Proyecto fin de grado Gradu amaierako proiektua

Application Acceleration Using a Heterogeneous MPSoC Architecture with MPU and FPGA Processors

Mikel Solabarrieta Román

Director: Ignacio Angulo Martínez

Bilbao, junio de 2020

Facultad de Ingeniería Universidad de Deusto

**Ingeniaritza Fakultatea** Deustuko Unibertsitatea

# Grado en Ingeniería en Electrónica Industrial y Automática Industria Elektronikako eta Automatikako Ingeniaritzako Gradua

# Proyecto fin de grado Gradu amaierako proiektua

Application Acceleration Using a Heterogeneous MPSoC Architecture with MPU and FPGA Processors

Mikel Solabarrieta Román

Director: Ignacio Angulo Martínez

Bilbao, junio de 2020

hart

## Abstract

This degree thesis tests the performance improvements of an MPU+FPGA multiprocessor systemon-chip (MPSoC) over standard microcontrollers in edge computing applications, namely object detection and facial recognition. Conclusions are deducted from execution profiles of similar facial recognition applications with and without FPGA acceleration.

The board used for this thesis is a Xilinx Zynq UltraScale+ MPSoC development board: the Ultra96-v1.

A brief description of Zynq is due before describing the application it will be used for. Zynq is a computer architecture designed by Xilinx that contains both an ARM processor and a Field-Programmable Gate Array. PYNQ is a Zynq framework that has been used to develop software for this thesis mainly because it allows the usage of the Python programming language to make use of Zynq. It runs on the Linux operating system and has Jupyter Notebooks installed by default. Programmable Logic is implemented with overlays: hardware libraries that enable a simple way of interacting with the FPGA.

Facial recognition and object detection are both relatively computationally heavy tasks that tasks a lot of time to perform on standard microcontrollers. The viability of performing the aforementioned tasks in real time will be tested by using existing overlays to accelerate Artificial Intelligence algorithms and computer vision utilities, both independently and integrating them.

#### Descriptors

Edge Computing, Embedded Devices, MPSoC, PYNQ, Zynq

# Contents

| 1 | Intr | roduction                 | 1  |

|---|------|---------------------------|----|

|   | 1.1  | Context                   | 1  |

|   | 1.2  | Project Motivation        | 1  |

|   | 1.3  | Problem and Need          | 2  |

|   | 1.4  | Justification             | 3  |

| 2 | Sco  | ре                        | 5  |

|   | 2.1  | Ethical Considerations    | 6  |

|   | 2.2  | Objectives                | 6  |

|   | 2.3  | Project Structure         | 7  |

| 3 | Tec  | hnical Requirements       | 9  |

|   | 3.1  | Functional Objectives     | 9  |

|   | 3.2  | Non-Functional Objectives | 11 |

| 4 | Met  | thodology and Resources   | 15 |

|   | 4.1  | Kanban                    | 15 |

|   | 4.2  | Resources                 | 16 |

| 5 | Buc  | lget and Planning         | 19 |

|   | 5.1  | Budget                    | 19 |

|   | 5.2  | Planning                  | 20 |

| 6 | Stat                                          | e of the Art                                                                                                                                                                                                                                                                 | 23                                                                                                                     |

|---|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   | 6.1                                           | Key Areas                                                                                                                                                                                                                                                                    | 23                                                                                                                     |

|   |                                               | 6.1.1 Edge Computing                                                                                                                                                                                                                                                         | 24                                                                                                                     |

|   |                                               | 6.1.2 System-on-Chip                                                                                                                                                                                                                                                         | 24                                                                                                                     |

|   | 6.2                                           | Platform Overview                                                                                                                                                                                                                                                            | 24                                                                                                                     |

|   |                                               | 6.2.1 Zynq                                                                                                                                                                                                                                                                   | 25                                                                                                                     |

|   |                                               | 6.2.2 PYNQ                                                                                                                                                                                                                                                                   | 28                                                                                                                     |

|   | 6.3                                           | Board Overview                                                                                                                                                                                                                                                               | 33                                                                                                                     |

|   | 6.4                                           | High-Level Synthesis                                                                                                                                                                                                                                                         | 35                                                                                                                     |

|   | 6.5                                           | Preceding Projects                                                                                                                                                                                                                                                           | 36                                                                                                                     |

|   |                                               | 6.5.1 FINN                                                                                                                                                                                                                                                                   | 36                                                                                                                     |

|   |                                               | 6.5.2 Binarized Neural Networks                                                                                                                                                                                                                                              | 37                                                                                                                     |

|   |                                               | 6.5.3 Quantized Neural Networks                                                                                                                                                                                                                                              | 39                                                                                                                     |

|   |                                               |                                                                                                                                                                                                                                                                              |                                                                                                                        |

| 7 | Dev                                           | elopment                                                                                                                                                                                                                                                                     | 41                                                                                                                     |

| 7 | <b>Dev</b><br>7.1                             | e <b>lopment</b><br>Familiarization with the PYNQ Platform                                                                                                                                                                                                                   | <b>41</b><br>41                                                                                                        |

| 7 |                                               |                                                                                                                                                                                                                                                                              |                                                                                                                        |

| 7 | 7.1                                           | Familiarization with the PYNQ Platform                                                                                                                                                                                                                                       | 41                                                                                                                     |

| 7 | 7.1                                           | Familiarization with the PYNQ Platform       Familiarization         Facial Recognition       Familiarization                                                                                                                                                                | 41<br>42                                                                                                               |

| 7 | 7.1                                           | Familiarization with the PYNQ Platform    Familiarization      Facial Recognition    Familiarization      7.2.1    LFC Setup                                                                                                                                                 | 41<br>42<br>42                                                                                                         |

| 7 | 7.1                                           | Familiarization with the PYNQ Platform                                                                                                                                                                                                                                       | <ul> <li>41</li> <li>42</li> <li>42</li> <li>46</li> </ul>                                                             |

| 7 | 7.1                                           | Familiarization with the PYNQ Platform                                                                                                                                                                                                                                       | <ul> <li>41</li> <li>42</li> <li>42</li> <li>46</li> <li>48</li> </ul>                                                 |

| 7 | 7.1                                           | Familiarization with the PYNQ Platform                                                                                                                                                                                                                                       | <ol> <li>41</li> <li>42</li> <li>42</li> <li>46</li> <li>48</li> <li>49</li> </ol>                                     |

| 7 | 7.1                                           | Familiarization with the PYNQ Platform                                                                                                                                                                                                                                       | <ol> <li>41</li> <li>42</li> <li>42</li> <li>46</li> <li>48</li> <li>49</li> <li>50</li> </ol>                         |

| 7 | 7.1<br>7.2                                    | Familiarization with the PYNQ Platform         Facial Recognition         7.2.1       LFC Setup         7.2.2       LFC Usage         7.2.3       CNV Setup         7.2.4       CNV Usage         Object Detection                                                           | <ol> <li>41</li> <li>42</li> <li>42</li> <li>46</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> </ol>             |

| 7 | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Familiarization with the PYNQ Platform         Facial Recognition         7.2.1       LFC Setup         7.2.2       LFC Usage         7.2.3       CNV Setup         7.2.4       CNV Usage         Object       Detection         7.3.1       Setup         7.3.2       Usage | <ol> <li>41</li> <li>42</li> <li>42</li> <li>46</li> <li>48</li> <li>49</li> <li>50</li> <li>50</li> <li>51</li> </ol> |

#### 8 Results

| 9            | O Conclusions           | 65 |

|--------------|-------------------------|----|

|              | 9.1 Future Work         | 66 |

|              | 9.2 Personal Assessment | 67 |

| Bi           | Bibliography            | 71 |

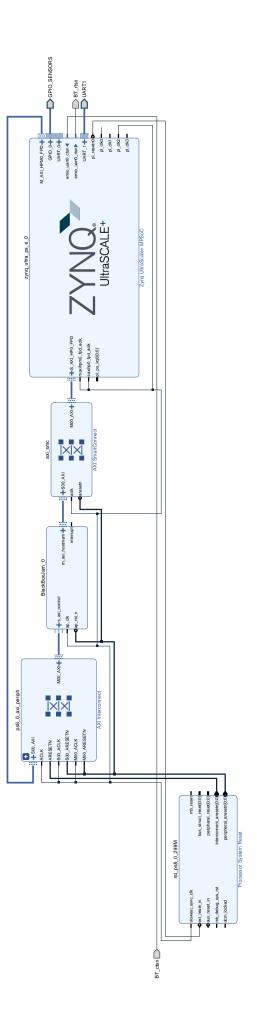

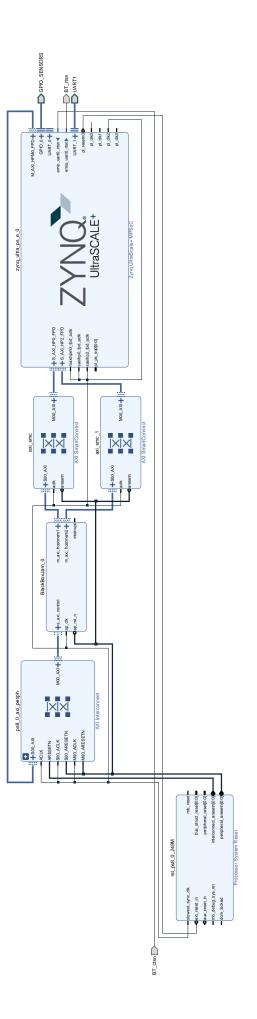

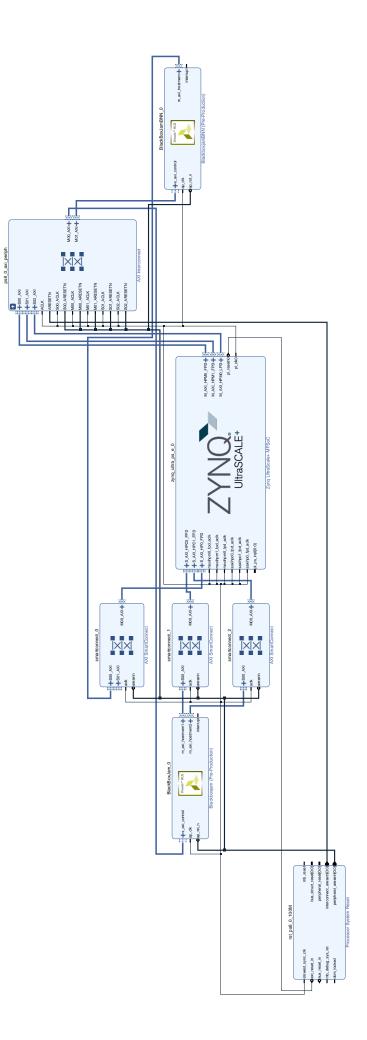

| $\mathbf{A}$ | A Vivado Block Designs  |    |

#### **B** Integration Utilization Report

### C HLS Example

# List of Figures

| 1.1  | Profile of object detection program                        | 2  |

|------|------------------------------------------------------------|----|

| 2.1  | Characteristics of the BSD-3 license used for PYNQ         | 6  |

| 2.2  | Project structure                                          | 8  |

| 4.1  | Kanban board                                               | 15 |

| 4.2  | Picture of the PYNQ-Z1 (left) and Ultra96 (right) boards   | 17 |

| 5.1  | Project schedule                                           | 22 |

| 6.1  | Zynq-7000 architectural overview                           | 25 |

| 6.2  | Zynq-UltraScale+ component overview                        | 26 |

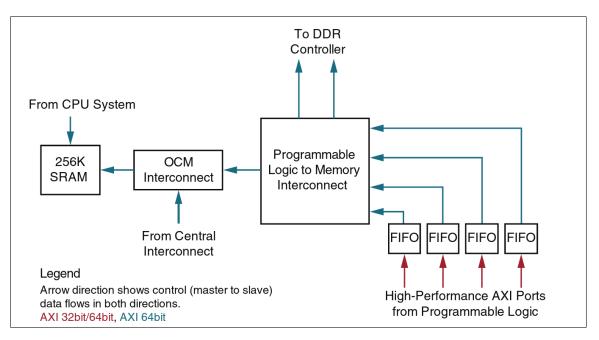

| 6.3  | PL interface to PS memory                                  | 27 |

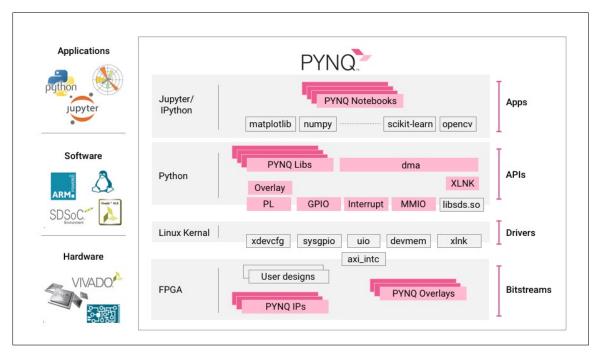

| 6.4  | PYNQ application overview                                  | 28 |

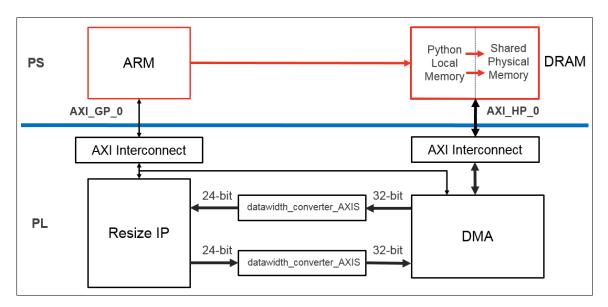

| 6.5  | State of the program with image in local and shared memory | 30 |

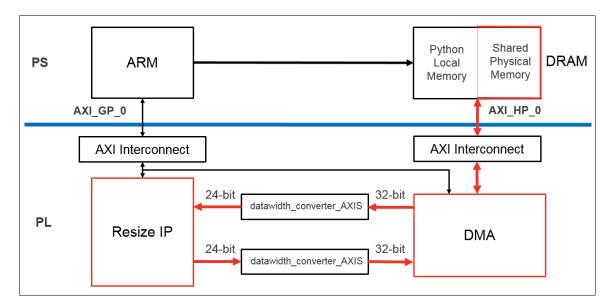

| 6.6  | State of the program when using the PL                     | 31 |

| 6.7  | Jupyter Notebook example                                   | 32 |

| 6.8  | Picture of the Ultra96-v1 board                            | 33 |

| 6.9  | PS specifications                                          | 34 |

| 6.10 | PL specifications                                          | 34 |

| 6.11 | Ultra96 block diagram                                      | 35 |

| 6.12 | HLS validation and verification                            | 36 |

| 6.13 | FINN data flow                                             | 38 |

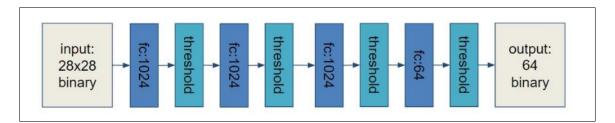

| 6.14 | LFC diagram                                                  | 39 |

|------|--------------------------------------------------------------|----|

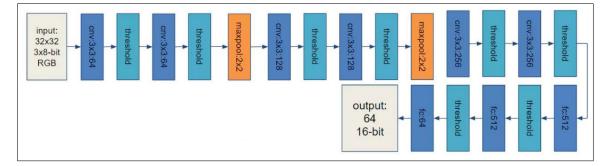

| 6.15 | CNV diagram                                                  | 39 |

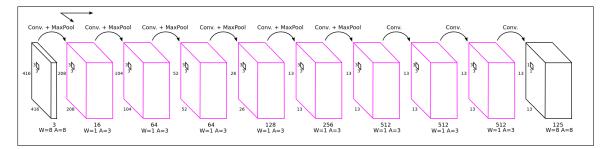

| 6.16 | TinierYOLO topology                                          | 40 |

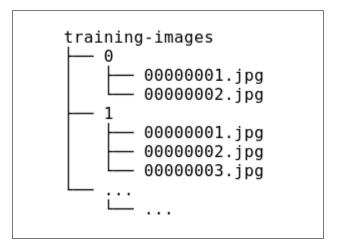

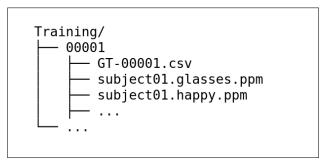

| 7.1  | Dataset directory structure                                  | 43 |

| 7.2  | Best epoch when training LFCW1A2                             | 46 |

| 7.3  | GTSRB modified dataset directory structure                   | 48 |

| 7.4  | Best epoch when training CNVW1A1                             | 49 |

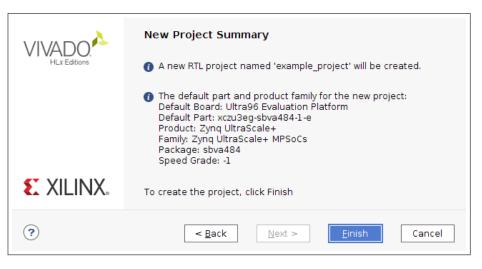

| 7.5  | Last step before creating the Vivado project                 | 56 |

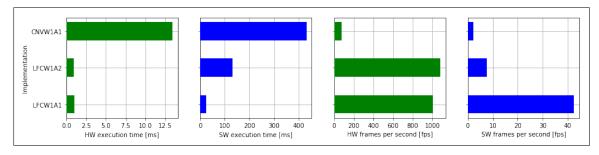

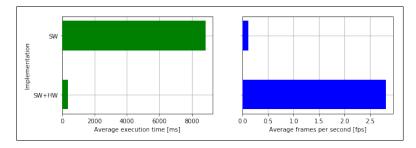

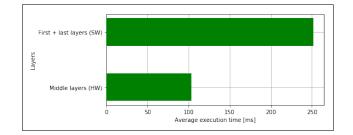

| 8.1  | Execution times of each BNN topology                         | 62 |

| 8.2  | Alternative view of the execution times of each BNN topology | 62 |

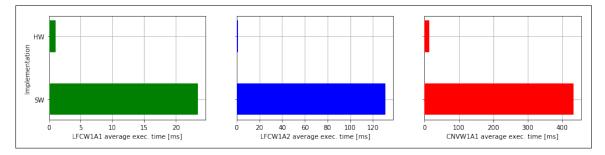

| 8.3  | Comparison of HW+SW and SW QNN execution times               | 63 |

| 8.4  | Comparison of border (SW) and middle (HW) layers             | 63 |

| 8.5  | GitLab repository containing the Jupyter Notebooks           | 64 |

# List of Tables

| 3.1 | Requirements of objective O1 | 9  |

|-----|------------------------------|----|

| 3.2 | Requirements of objective O2 | 10 |

| 3.3 | Requirements of objective O3 | 10 |

| 3.4 | Requirements of objective O4 | 11 |

| 3.5 | Requirements of objective O5 | 11 |

| 3.6 | Requirements of objective O6 | 12 |

| 3.7 | Requirements of objective O7 | 12 |

| 3.8 | Requirements of objective O8 | 12 |

| 3.9 | Requirements of objective O9 | 13 |

| ۳ 1 |                              | 10 |

| 5.1 | Cost of human resources      | 19 |

| 5.2 | Cost of material resources   | 20 |

# Listings

| 6.1  | "IP extraction from the resizer overlay"      | 29 |

|------|-----------------------------------------------|----|

| 6.2  | "Memory allocation"                           | 29 |

| 6.3  | "PL usage"                                    | 30 |

| 7.1  | "Image modification script"                   | 44 |

| 7.2  | "Sample of mnist.py"                          | 45 |

| 7.3  | "Module versions"                             | 45 |

| 7.4  | "BNN LFC usage example"                       | 46 |

| 7.5  | "PynqBNN constructor"                         | 47 |

| 7.6  | "Training of CNV"                             | 48 |

| 7.7  | "BNN usage example"                           | 49 |

| 7.8  | "Ctypes example from darknet.py"              | 50 |

| 7.9  | "Python dynamic library import in darknet.py" | 51 |

| 7.10 | "Function definition example from darknet.py" | 51 |

| 7.11 | "QNN global variables"                        | 51 |

| 7.12 | "QNN imports"                                 | 52 |

| 7.13 | "Partial method of TinierYolo class"          | 52 |

| 7.14 | "Network architecture"                        | 52 |

| 7.15 | Network creation and configuration"           | 53 |

| 7.16 | "First QNN layer"                             | 53 |

| 7.17 | "Middle QNN layers"                           | 54 |

| 7.18 | "Middle QNN layers post-processing"           | 54 |

| 7.19 | "Extraction of results from QNN"              | 54 |

| 8.1  |                                               | 63 |

### Chapter 1

## Introduction

This thesis aims to provide relevant information about the end of degree project. This chapter intends to provide an introduction to the project, provide context for it, the motivation behind it and lay out the problem it intends to solve.

#### 1.1 Context

The rise of Internet of Things (IoT) systems for any range of applications, from industrial to consumer ones, brings with it the benefit of bringing "intelligence" to applications that didn't traditionally have it. IoT, in this context, is described as the convergence of technologies from the fields of data-capture devices, embedded systems and analytics, amongst others.

Inside IoT systems, edge computing consists on running some of the data-processing functions in the data-capture devices themselves rather than in centralized servers. Dual architectures such as the one provided by Xilinx enable edge devices, devices that do the processing, to be more flexible and more efficient regarding both computation and energy consumption than a standard, single-processor device. The advantages of this specific paradigm were a device with ARM+FPGA processors are used for edge computing include speed improvements, reduced bandwidth use and energy consumption, some security improvements and increased reliability. While there are some downsides, such as the increased programming difficulty, in most cases they are outweighed by the benefits.

#### **1.2** Project Motivation

The adoption of an interesting, relatively new architecture with potential implications in fields such as Distributed Systems, Edge Computing and High Performance Computing. As discussed in the "Justification" section, the fact that the platform studied in this project seems to be the path many researchers and professionals will take is a great motivator. The interest in a research career

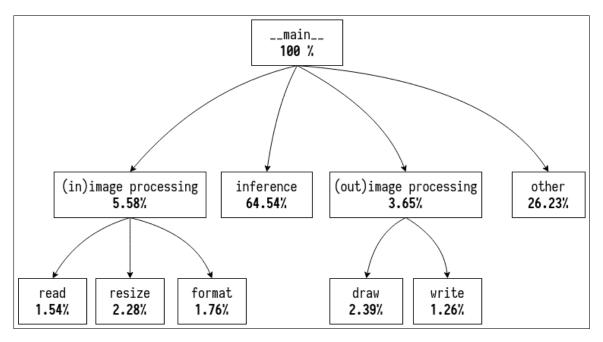

Fig. 1.1: Profile of object detection program

and both personal and professional interests in fields very related to this project, such as High Performance Computing (HPC) are also important factors. This will be the last project before pursuing a career in the HPC field, thus exploring what the personally completely new concept that is a heterogeneous, dual architecture that combines many of the interests adjured during the studies is appropriate.

One of the firsts steps of the project was to run an object detection application in a computer with an ARM processor and profile the execution. Figure 1.1 shows a simplified version of the profile. The program run the facial recognition function in 43 different images and, as seen in the image, a highly parallelizable section of the code: the inference, was taking more than half of the execution times. The code section shown in the picture as "other" included displaying the images, which if handled correctly with concurrency could completely disappear from the profile. It is clear then the potential of a device such as the one studied in this project: the performance can be very significantly improved without the developer of the application needing to know the inner workings of any low-lever level device. Just take the input, pass it to the PL, and receive the output. This is significantly important in industrial environments where reducing the latency of error detection in any process can prevent downtime and lead to considerable savings.

### 1.3 Problem and Need

The way IoT technologies are currently implemented has a lot of room for improvement, such as the centralization of processing units and the need to send great amounts of data from the acquisition systems to the processing units potentially saturating the networking infrastructure. While solutions to some of the presented problems exist, most noticeable the development and deployment of 5G networking infrastructure, the Zynq architecture could prove to be an impactful and further improve the situation when combined with other solutions.

Reiterating, the problem is that most edge devices have low computing power and can't run advanced processes on the data, requiring to be sent to central servers. Thus the need is an edge computing device that allows for such processing while being energy efficient and low cost. This project specifically looks at an edge computing device able of performing object detection and facial recognition without requiring the transmission of video feed to central servers or introducing latency and bandwidth issues to the network. Both of these applications are computationally heavy and can't be adequately performed in real-time by standard microcontrollers that have acceptable energy consumption. The dual ARM+FPGA enables the delegation of computationally heavy tasks that can be parallelized to the FPGA processing unit while implementing the rest of the functionality in the ARM processors. This project evaluates how the Zynq architecture and the PYNQ framework work as a solution to this problem.

#### 1.4 Justification

The idea that specialized hardware is becoming increasingly relevant in multiple fields, albeit not a definitive solution to problems that require more flexibility, is a justifying argument in itself. The counter-argument: that some problems require a more flexible solution, can also be turned around in this specific case. The processor-centric approach means that designs downloaded to the FPGA can be changed on runtime, which brings flexibility single processor devices lack.

Despite being the final project of the Industrial Electronics and Automation Engineering degree, it involves concepts studied in both degrees of the double degree. The main approach is based on using an ARM processor, which combined with an FPGA in a single MPSoC device gives very significant performance improvements. The platform is intended for industrial uses and could have been applied in many of the degree subjects: signal processing, automatizing... Because it contains many different subjects studied throughout the degree, it seems appropriate as a final project for the electronics degree. At the same time, development is made more accessible by using a framework based on GNU/Linux and Python, both of which have been very relevant subjects in the Computer Engineering degree. The knowledge acquired about the GNU/Linux operating systems has proven useful not only for understanding the platform better but also for troubleshooting in several steps of the project development process. Knowledge of Python has also proven very useful in several sections were documentation was lacking and the provided code needed to be thoroughly inspected. It has also been useful to speed up development and modify things such as code of broken dependencies. At a certain point in the project, the C development done in the microcontrollers and automatizing subjects electronics degree also proved useful when modifying a library that while called from Python, was written in C. This will be discussed further in one of the final sections, section 9.2.

### Chapter 2

## Scope

The main goal of this project is to research and experiment with the state of the art technology that represents the PYNQ framework and its underlying technology, and its actual and potential impact on relevant applications. These applications are in this case object detection and facial recognition because, as explained in the introduction chapter, they are recurrent processes in countless scenarios and computationally demanding for most standard microcontrollers. They represent an example of how the range of data-processing functions that can be executed by devices near to where the data is captured instead of in central servers is not limited to basic operations and can have some level of complexity. Experimenting with these examples is, once again, the goal of this project and both the scope and the results are oriented to representing so.

Some concepts, such as "overlays" are mentioned in this chapter and in chapter 3 are not explained until chapter 6 but should be clear after reading it.

The expected final result of the project includes:

- Analysis of the Zynq architecture

- Analysis of existing PYNQ projects and their potential use in object detection and face recognition

- Adaptation of the existing PYNQ project to fit the use cases of object detection and face recognition

- Benchmarks of multiple hardware-accelerated applications and their not accelerated versions

- A program integrating various PYNQ overlays to meet the requirements of real-time object detection and face recognition in an edge computing device

#### 2.1 Ethical Considerations

The first ethical aspect examined is software licensing. Software licenses determine what people can do with software, how they can use, modify and distribute it; and are often overlooked. Many of the components of this project have open licenses, namely the BSD-3 or "BSD new" license, its most relevant characteristic being the ability to modify and redistribute the source code as long as the original license is included. It is compatible with the widely used GNU General Public License and has some more specific details, such as forbidding the use of the names of the original authors for endorsements. The main characteristics of the license are listed in figure 2.1. Having a permissive software license is important because it gives more rights and opportunities to anyone interested in using the software, favoring accessibility and equality.

Fig. 2.1: Characteristics of the BSD-3 license used for PYNQ

Other ethical aspects of special relevance to this project are the potential uses of facial recognition and object detection. Facial recognition is a technology with many potential benefits, but also many risks. Due to this, many of the companies and institutions developing the technology are doing it with caution. While acknowledging the clear benefits it may offer (convenience, security...), this section will focus on analyzing the ethical issues it presents. The most commonly discussed risks are the privacy issues systems using facial recognition may imply, or the potential exploitation of the ability to instantly identify people. Assessing privacy issues, facial recognition is often used without the consent of the people being analyzed; and in some cases can be used to access a lot of public information about a person with just their face, even if that person did not agree to it. About exploitation, the ability to identify people instantly can be used for unethical purposes, for example by a government or company running a face recognition algorithm against a group of protesting people to identify and retaliate against them. When applied to critical applications such as automated criminal identification, false positives may result in innocent people being condemned which goes against the principle of justice.

It is important that the ethical issues of these applications are analyzed and regulated. Questions must be asked about why certain technologies are being developed and what potential risks they may have and how those affect people or the environment, before developing them.

#### 2.2 Objectives

The main objective of the project is to evaluate how suitable the Zynq devices with the PYNQ framework are as a solution to the necessities edge computing presents in modern IoT systems.

Two computationally heavy tasks will be studied: object detection and facial recognition. As mentioned previously, these two tasks are too demanding for standard, mainstream homogeneous (mono-core or multi-core) embedded microcontrollers.

Functional objectives:

- O1 An independent application must be able to identify a person's face given a frame.

- O2 An independent application must be able to detect objects given a frame.

- O3 An integrated application must be able to perform both previous tasks.

Non-functional objectives:

- **O4** Tasks must be able to be performed in real time, each one of them processing at least 5 frames per second.

- **O5** Code must be deployable in PYNQ-enabled Ultra96-v1 device.

- O6 Accelerated processes must be noticeably faster than their pure software versions.

- O7 The code must be clear and understandable.

- **O8** Documentation must be provided for the resulting code and underlying ideas.

- **O9** Software licenses must be compatible.

#### 2.3 Project Structure

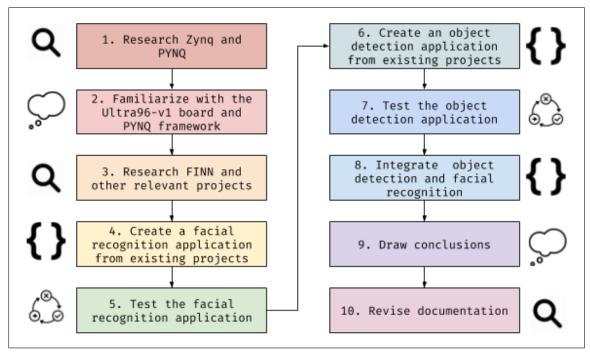

The structure of the project is shown in figure 2.2, and contains the following steps. Summarizing, it consists on researching state-of-the art technology and areas and trying them in different use cases, before trying to combine them into the intended final use.

Fig. 2.2: Project structure

- 1. **Research Zynq and PYNQ.** Research Zynq architecture and the PYNQ framework. Understand their purpose and how they work.

- 2. Familiarize with the Ultra96-v1 board and PYNQ framework. The Ultra96-v1 is the physical device that runs PYNQ in this project.

- 3. Research FINN and other relevant projects. Research projects built over PYNQ that will be used in the next steps.

- 4. Create a facial recognition application from existing projects. Adapt an existing project to serve the facial recognition functionality.

- 5. Test the facial recognition application. Test the efficiency of the facial recognition solution.

- 6. Create an object detection application from existing projects. Adapt an existing project to serve the object detection functionality.

- 7. Test the object detection application. Test the efficiency of the object detection solution.

- 8. Integrate object detection and facial recognition. Integrate the previous solutions into a single project that meets all the requirements of the project.

- 9. Draw conclusions. Analyze the project and extract conclusions.

- 10. Revise documentation. Finish the project documentation.

The project structure will be further analyzed when detailing the objectives in chapter 3 and in the planning of chapter 5, which details how much time and resources will be dedicated to each one of the tasks.

### Chapter 3

## **Technical Requirements**

This chapter defines and explains each of the requirements of the project based on objectives from section 2.2. Each objective has certain requirements. Each requirement is fully identified by appending the requirement identifier to the objective identifier. Thus, the full identifier for requirement **R1** of objective **O1** is **O1R1**. Requirements that require additional specifications have a specification section. Specifications are fully identified by appending the objective, requirement and specification identifiers.

### 3.1 Functional Objectives

#### **Objective 1**

The first objective, **O1** refers to the facial recognition functionality and states that an application must be created to receive a frame as input and output what person the face belongs to.

| Requirement      |                                                                                                |  |  |

|------------------|------------------------------------------------------------------------------------------------|--|--|

| R1 Functional    | $\mathbf{R1}$ Functional PYNQ overlay that runs a picture through an AI classifier and outputs |  |  |

| the class the p  | icture belongs to.                                                                             |  |  |

| Specification    | Specification Description                                                                      |  |  |

| S1               | S1 The overlay must fit in the Ultra96-v1 board.                                               |  |  |

| Requirement      | Requirement                                                                                    |  |  |

| R2 Functional    | ${f R2}$ Functional Python program that provides a provides an image as input to the overlay   |  |  |

| and displays the | and displays the output in a readable manner.                                                  |  |  |

Table 3.1: Requirements of objective O1

### Objective 2

The second objective, **O2** details that an object detection algorithm must be accelerated with the Zynq architecture. All sections of code that are likely to offer a substantial improvement when accelerated by hardware must be implemented using programmable logic (PL) and those that cannot be accelerated must be efficiently implemented in Python.

| Table 3.2: Requirements | of objective O2 |

|-------------------------|-----------------|

|-------------------------|-----------------|

| Requirement               |                                                                                              |  |  |

|---------------------------|----------------------------------------------------------------------------------------------|--|--|

| R1 Functional             | PYNQ overlay that runs a picture through an AI classifier and outputs                        |  |  |

| a bounding bo             | x of each object detected in the picture.                                                    |  |  |

| Specification             | Description                                                                                  |  |  |

| <b>S</b> 1                | S1 The overlay must fit in the Ultra96-v1 board.                                             |  |  |

| Requirement               | Requirement                                                                                  |  |  |

| R2 Functional             | ${f R2}$ Functional Python program that provides a provides an image as input to the overlay |  |  |

| and filters the           | and filters the bounding boxes outputted by the overlay that belong to people.               |  |  |

| Specification Description |                                                                                              |  |  |

| <b>S</b> 1                | <b>S1</b> The Python program must for compensate any functionalities the overlay             |  |  |

|                           | lacks.                                                                                       |  |  |

#### **Objective 3**

Objective 3 or **O3** refers to a program that combines the functionality of object detection and facial recognition, effectively detecting and recognizing people in an image. The ideal solution is an overlay with functions that do both as specified in requirement **O3R1**, however that is a complicated task that may fail. With that in mind, an alternative program design must be provided as stated in requirement **03R2**.

Table 3.3: Requirements of objective O3

| Requirement          |                                                                                   |  |

|----------------------|-----------------------------------------------------------------------------------|--|

| R2 Functional        | PYNQ overlay that combines <b>O1R1</b> and <b>O2R1</b>                            |  |

| Specification        | Description                                                                       |  |

| <b>S</b> 1           | The overlay must fit in the Ultra96-v1 board.                                     |  |

| S2                   | The functions corresponding to each functionality must be provided sep-           |  |

|                      | arately.                                                                          |  |

| Requirement          | Requirement                                                                       |  |

| R3 If O3R1           | R3 If O3R1 cannot be met an alternative program must be provided that effectively |  |

| utilizes <b>O1R1</b> | utilizes $\mathbf{O1R1}$ and $\mathbf{O2R1}$ to achieve the same functionality.   |  |

| Specification        | Specification Description                                                         |  |

| <b>S</b> 1           | <b>S1</b> The program must minimize the performance impact of not achieving       |  |

|                      | O3R1.                                                                             |  |

| Requirement          | Requirement                                                                       |  |

**R3** Python program that wraps **O3R1**, feeds the overlays their corresponding inputs and manages the outputs. If **O3R1** is not met, the **O3R3** must wrap **O3R2**.

### 3.2 Non-Functional Objectives

#### **Objective 4**

Objective **O4** defines what is considered "real-time" in this project and does so as a minimum of 3 frames per second for application.

|               | Requirement                                                                      |  |

|---------------|----------------------------------------------------------------------------------|--|

| R1 The image  | e processing part of each application must be able to process 3 frames per       |  |

| second.       | second.                                                                          |  |

| Specification | Specification Description                                                        |  |

| <b>S</b> 1    | S1 Image processing is measured, but not image capture or posterior man-         |  |

|               | agement.                                                                         |  |

| S2            | <b>S2</b> FPS can be extrapolated from single measures or averaged from multiple |  |

|               | processing of consecutive frames to counter potential bottlenecks.               |  |

| Table $3.4$ : | Requirements | of objective O4 |

|---------------|--------------|-----------------|

|---------------|--------------|-----------------|

#### **Objective 5**

Objective **O5** defines that the developed programs must be deployable in any PYNQ-enabled Ultra96-v1 board.

| Table $3.5$ : | Requirements | of objective O5 |

|---------------|--------------|-----------------|

|---------------|--------------|-----------------|

| Requirement                                                                                 |                                                                   |  |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| <b>R1</b> Following the steps in chapter 7 any of the applications must be deployable in an |                                                                   |  |

| Ultra96-v1 board with the PYNQ firmware.                                                    |                                                                   |  |

| Specification                                                                               | Description                                                       |  |

| <b>S</b> 1                                                                                  | The firmware version used in development is specified.            |  |

| S2                                                                                          | 2 The code is publicly available.                                 |  |

| <b>S</b> 3                                                                                  | Either the training materials or trained models are provided.     |  |

| <b>S</b> 4                                                                                  | Installation scripts for some steps are provided for convenience. |  |

#### **Objective 6**

Objective **O6** states that each accelerated component must have a non-accelerated counterpart to compare it to, and the HW version must perform better than the HW version.

#### Table 3.6: Requirements of objective O6

|                                                                                                  | Requirement                                                                             |  |  |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| R1 A pure so                                                                                     | R1 A pure software implementation must be provided for each hardware-accelerated        |  |  |

| part. The fund                                                                                   | part. The functionality and internal logic of the SW versions must be comparable to the |  |  |

| HW ones.                                                                                         |                                                                                         |  |  |

| Specification                                                                                    | Description                                                                             |  |  |

| <b>S</b> 1                                                                                       | Each of the applications must also have a pure software implementation.                 |  |  |

| S2                                                                                               | The SW implementation must work similarly to the HW one.                                |  |  |

| S3                                                                                               | S3 Benchmarks will compare both versions.                                               |  |  |

| Requirement                                                                                      |                                                                                         |  |  |

| $\mathbf{R2}$ Accelerated versions must have an execution time that is at least 60% smalled than |                                                                                         |  |  |

| the non-accelerated version.                                                                     |                                                                                         |  |  |

### Objective 7

Objective **O7** states that the code must be clear and understandable.

Table 3.7: Requirements of objective O7

| Requirement                                                     |                                                        |  |

|-----------------------------------------------------------------|--------------------------------------------------------|--|

| <b>R1</b> The code must be consistent and as clear as possible. |                                                        |  |

| Specification                                                   | Description                                            |  |

| <b>S</b> 1                                                      | Function, type and variable names must be descriptive. |  |

| S2                                                              | Code syntax must be consistent within each program.    |  |

| <b>S</b> 3                                                      | Comments must clarify relevant sections of the code.   |  |

### Objective 8

Objective  ${\bf O8}$  states that the programs and underlying ideas must be documented.

#### Table 3.8: Requirements of objective O8

| Requirement                                                                              |                                                                                                  |  |  |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|

| R1 Jupyter No                                                                            | $\mathbf{R1}$ Jupyter Notebooks detailing the steps followed in the program must be provided for |  |  |

| each one of the applications.                                                            |                                                                                                  |  |  |

| Specification                                                                            | Description                                                                                      |  |  |

| <b>S</b> 1                                                                               | A single Jupyter Notebook must be provided for each application.                                 |  |  |

| S2                                                                                       | The notebook must detail what is being done and why.                                             |  |  |

| Requirement                                                                              |                                                                                                  |  |  |

| ${f R1}$ The ideas behind the programs and the development documentation must be present |                                                                                                  |  |  |

| in the state of the art and development sections of this document. Sections are chapters |                                                                                                  |  |  |

| 6 and 7 respectively.                                                                    |                                                                                                  |  |  |

#### **Objective 9**

Objective **O9** defines that the licenses given to the results of this project must be compatible with the ones of the dependencies and each other.

#### Table 3.9: Requirements of objective O9

Requirement

R1 The software licenses of the results must be compatible with the ones of the sources and libraries. There must be no licensing conflicts.

## Chapter 4

## Methodology and Resources

#### 4.1 Kanban

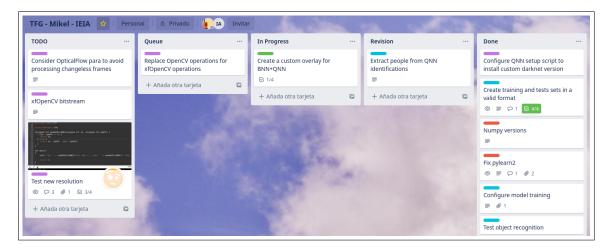

Kanban methodology was used during the development of the project. Kanban comes from a procedure that was used to track the route of a product throughout a factory. Similarly, the current Kanban methodology tracks the state of tasks in a project. The methodology and word have Japanese origin, "kan" meaning "visual" and "ban" meaning "card".

The Kanban methodology is based on a board. The board gives all the necessary information about the state of each task. It provides a convenient, quick way of determining the state of the project or how it is doing regarding the pacification. It also provides "agile" flexibility to the project as tasks can be easily and quickly moved or adapted depending on the requirements. Tasks in Kanban are assigned to cards. Cards are placed in columns. In this specific project, five columns were used. Columns are ordered and contain any number of cards. Cards can be moved from one column to any adjacent column. Figure 4.1 shows a screenshot of the Kanban board at one point of the project.

Fig. 4.1: Kanban board

Instead of a physical board, a digital one provided by Trello was used, also seen in the screenshot of figure 4.1. The Trello version that was used is free, provides many functionalities, team and organizational capabilities. Each tasks can be commented on, contain checklists, media, descriptions and so on. It also has integration with many services including the ones of its parent company Atlassian or others such as GitHub. Although these integration were not used in this project, they are still useful and worth mentioning. This is specially true when considering a lot of software developers use this methodology as means of development and communication with clients in the form of issues, which are user requests sometimes turned into tasks.

The five columns used in this project are listed below. The usual life cycle of a task starts in the first column and ends in the last, having gone through each other column in between at least one.

- **TODO**. This column contains tasks that have not been done yet and are not intended to be carried out in short term.

- Queue. The queue contains the tasks that have not been done yet but are intended to be carried out in the short term. Tasks are moved from Queue to the column to the right when started.

- In Progress. Contains all the tasks being currently under development.

- **Revision**. Tasks in this column have been developed but need to be revised to ensure everything is correct.

- Done. Contains all the completed tasks.

#### 4.2 Resources

The human resources used for this project were the author, the director and an external consultant. The author and director will take many roles in the budget to more accurately convey the actual cost it would entail to have an engineer specialized in each field.

The digital resources will be analyzed in order of relevance. In the first place, the firmware, programming languages, frameworks, libraries and so on used during development. This includes PYNQ, interpreters and compilers... On second place, many Xilinx manuals were used. This, combined with multitude of articles about PYNQ applications and repositories such as BNN-PYNQ and QNN-MO-PYNQ was essential. All the code editing tools used in this project were free: Vim, Jupyter Notebooks and PyCharm. To edit this document, the Overleaf LaTeX editor was used with the template provided by the University of Deusto. Finally, the PYNQ forum was used to post a question regarding overlay compression, and even if no solution was found it was a helpful resource with great treatment and fast response times.

About physical resources, a Raspberry Pi 3 model B was used to run the initial programs in an ARM device. PYNQ experimentation began on a PYNQ-Z1 board but it was changed for a Ultra96-v1 board very early in the project. Access to both PYNQ boards, research and a lot of the development was done in a personal computer running GNU/Linux. The personal computer has

Fig. 4.2: Picture of the PYNQ-Z1 (left) and Ultra96 (right) boards

a GPU compatible with the machine learning model training libraries, which saved a considerable amount of ours. Vivado and other demanding software was all run in this computer. The boards were accessed either with Jupyter Notebooks or SSH.

### Chapter 5

## **Budget and Planning**

### 5.1 Budget

Table 5.1 shows the expected budget for human resources. There are four profiles: project director, researcher, developer and consultant. The project director coordinates the project and has an expected investment of 60 hours. The researcher profile handles research and documentation taking an expected amount 232 hours, while the developer writes, validates and tests the applications taking 120 expected hours. Consultant accounts for actual people who helped with the project either directly or through forums. The full schedule is detailed at section 5.2.

| Profile              | €/hour | Hours       | Total cost $[\mathbf{f}]$ |

|----------------------|--------|-------------|---------------------------|

| Project Director     | 45     | 60          | 2,700                     |

| Researcher (Student) | 38     | 232         | 8,816                     |

| Developer (Student)  | 36     | 120         | 4,320                     |

| Consultant           | 72     | 10          | 720                       |

|                      |        | Total cost: | 16,556                    |

Table 5.1: Cost of human resources

The material cost of the project represents the cost of the material acquired for the development of the project, in this case the PYNQ-Z1 board and the Ultra96-board. It should be stated that neither supposed a real personal cost and both were provided by the university. The material costs disregarding electrical costs are shown in table 5.2.

| Material   |             | Price (€) |

|------------|-------------|-----------|

| PYNQ-V1    |             | 199       |

| Ultra96-v1 |             | 259       |

|            | Total cost: | 458       |

Table 5.2: Cost of material resources

The total cost is therefore 17,014€.

#### 5.2 Planning

Figure 4.1 shows the expected schedule of the project. The schedule has been modified, although as little as possible. Sections about using certain libraries have been changed after choosing said library to fit them better. Decisions about linearity have also been made: although facial recognition and object detection could be developed in parallel, it was planned and done sequentially because it is more efficient for the researchers. The planning needed to take into account the documentation that was created during development.

Meetings with the project director took place weekly. These meetings consisted of discussing topics and results, reporting the state of the project and recent advancements and mapping out the immediate path to take afterwards. As a consequence of the *COVID-19* outbreak, remote meetings were had during great part of the project.

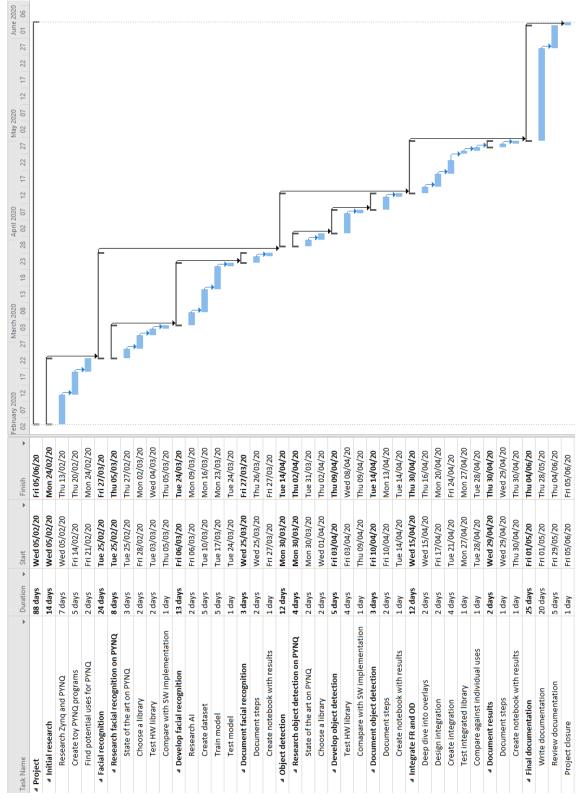

Figure 5.1 shows a Gantt diagram of the planned project schedule. The tasks correspond to the project structure explained in section 2.2. The first tasks of the project are centered around research and planning. The first development phase focuses on completing the facial recognition use case, while the second focuses on object detection. After that comes the integration of both use-cases, before writing the final documentation. Taking that into account, the following milestones can were defined:

- Research on the new technology. Expected start and finish dates: from 2020-02-05 to 2020-02-24. This phase involves learning about and familiarizing with the Zynq architecture and PYNQ framework. It is divided into three tasks: General research on the topics, the creation of simple programs for PYNQ and deciding what accelerated applications will be experimented next. Result: planning of the next steps.

- Facial recognition. Expected start and finish dates: from 2020-02-25 to 2020-03-27. This milestone will be reached when a functional facial recognition is successfully created and tested. With such a wide scope, it had to be split into thee sub-stages while each of the sub-stages is divided into multiple tasks. Sub-stages are explained next. Result: functional, accelerated facial recognition program.

- Research and library verification. Expected start and finish dates: from 2020-02-24 to 2020-03-05. This phase involves researching current developments on facial recognition applications on PYNQ or similar projects that could be useful for implementing it.

After the initial research, a library must be chosen, tested and benchmarked to enseure that results will be positive.

- Development. Expected start and finish dates: from 2020-03-06 to 2020-03-24. The library will likely need to be modified to serve the purpose of this project, which involves researching on the AI technology being used and how models can be trained. After that, a dataset needs to be created and the models trained, followed by validation and testing of the results.

- Documentation. Expected start and finish dates: from 2020-03-25 to 2020-03-27.

Steps followed in the previous sub-phases must be documented to be reproducible.

- **Object detection**. Expected start and finish dates: from 2020-03-30 to 2020-04-14. Similarly to the facial recognition milestone, this one marks the successful development of an object detection application. Steps are similar to the ones of facial recognition, but knowledge gained during the previous phase should prove useful and reduce the development time of this phase. Each of the sub-phases is described bellow. Result: functional, accelerated object detection program.

- Research and library verification. Expected start and finish dates: from 2020-03-30 to 2020-04-02. Research what the current state of the art is in object recognition on PYNQ, select a library and test it.

- Development. Expected start and finish dates: from 2020-04-03 to 2020-04-09. This sub-phase involves modifying the library to fit the use-case before validating and testing the results.

- Documentation. Expected start and finish dates: from 2020-04-10 to 2020-04-14.

This sub-phase involves documentation the entire phase to ensure previous steps reproducible.

- Integration of facial recognition and object detection. Expected start and finish dates: from 2020-04-15 to 2020-04-30. The goal of this phase is to integrate both use cases into a single application. The proposed way of doing so is by integrating both overlays into one, therefore overlays and overlay design need to be more thoroughly studied. After that, a new design will be created, validated and tested. Finally the application will be benchmarked. Tasks from research to validation are expected to take from 2020-04-15 to 2020-04-28. The steps need to be documented, which is expected to happen from 2020-04-29 to 2020-04-30. Result: integrated application of facial recognition and object detection.

- **Documentation**. Expected start and finish dates: from 2020-05-01 to 2020-06-04. This milestone represents the completion of the project documentation that will be delivered. It needs to be written, verified and corrected iterative. Result: project documentation.

Figure 5.1 shows an additional task at the end of the project: "Project closure". This involves preparing results by, for example, publishing private repositories were code was hosted during the development. The diagram shows a total of 88 days dedicated to the project, assuming four ours are dedicated each day. The amount of dedicated time will however depend on factors such as academical or professional workload. There is room for adjustment between the final day (June 3) and the thesis delivery deadline (June 24).

Fig. 5.1: Project schedule

## Chapter 6

# State of the Art

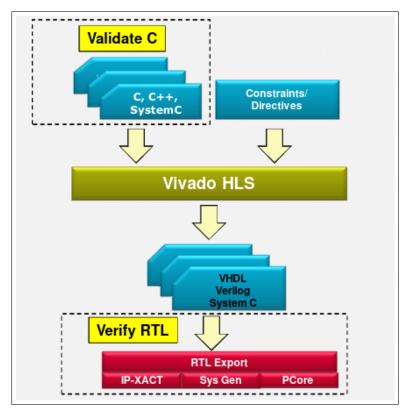

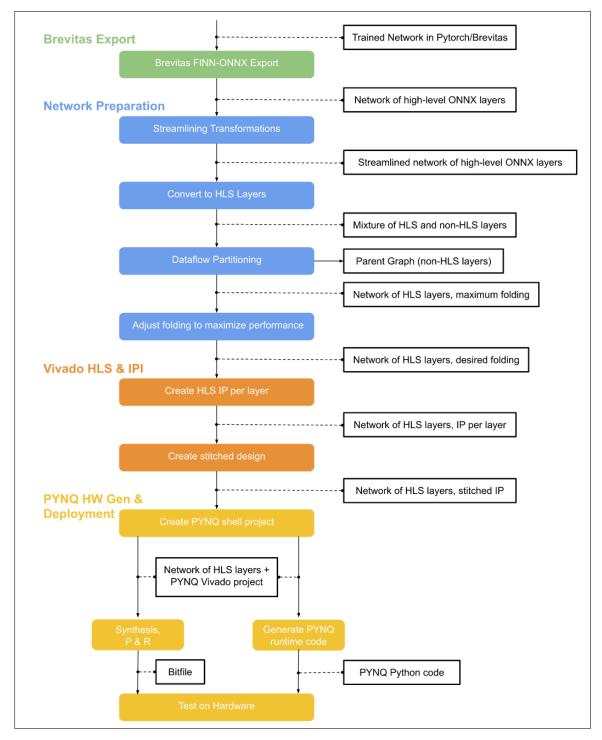

This section provides an overview to the relevant fields this project encompasses. Before continuing it is worth mentioning novelty of the adopted architecture and platform, and the studied projects such as FINN are the state of the art in the field of artificial vision in embedded devices. The other two analyzed topics in the "Preceding Projects" section are also pushing forward different scenarios where the platform provides performance advantages.

The platform is also innovative in another aspect: despite Despite the advanced knowledge in programmable logic, as well as in the architecture of the buses that allow the intercommunication between the processors and the FPGA, the PYNQ architecture is not only intended for people with knowledge on that area. If a "library" (it is not officially called library, but in this point the concept helps shedding a light on the idea) with the intended functionality exists, the programmer has only to download it to the PL and call it from C, or in this case Python, code. While still in development and maturing, the PYNQ platform and underlying technologies discussed in this section may have a great impact on future embedded devices.

## 6.1 Key Areas

This section discusses edge computing and SoC. These are two of the areas that might be more impacted by the success of Zynq and PYNQ. Edge Computing methodology and applications are currently designed majorly for non-accelerated embedded devices or local servers, but Zynq could mean that embedded devices are capable of running tasks currently assigned to local servers in specific, accelerate cases. Regarding SoCs, the way Zynq contains and communicates two heterogeneous processors could find greater adoption and research if Zynq (or PYNQ and therefore Zynq) gain even more traction.

#### 6.1.1 Edge Computing

Edge computing refers to a paradigm shift where data processing and storage of IoT applications are partially moved near where the data is acquired. It is not a new concept but is becoming increasingly popular with the rise of IoT related industries. In the context of this project, edge computing is done with low-power devices not comparable to the central servers of a service and thus lacking the required power to perform complex manipulations to the data. That however may change with the heterogeneous MPSoC architectures introduced in the SoC section. Edge computing can reduce the latency and broadband requirements of the system, as well as lighten the server load. The main advantage is clear: it benefits efficiency and flexibility. It may, however, involve increased complexity and risks. Each device adds more complexity to the overall system, which is specially true when each device is complex on itself. Adding more critical devices reduces the importance of each device, which translates to a reduced impact if a single device fails. From a security point of view, it also increases the attack surface of the system, aside from requiring new data policies (e.g. an edge computing with confidential data may be more vulnerable than central servers).

The benefits and shortcomings of edge computing should be analyzed for each application, but in this specific project, it is considered favorable as it would considerably reduce critical factors such as network saturation or latency. The device and platform examined from this point of view in this thesis: as potential edge computing devices that stand out from other products for their unique characteristics.

#### 6.1.2 System-on-Chip

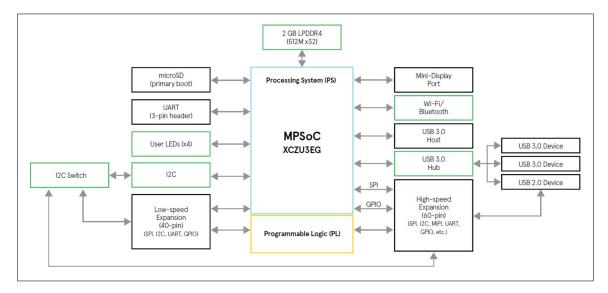

A System-on-Chip or SoC integrates the components of an electronic system in a single, integrated circuit. In the case of the Zynq architecture explained in section 6.2, the system contains an ARM processor, an FPGA, memory and IO components. Having multiple processing units means it is a Multiprocessor System-on-Chip or MPSoC. SoC is a common technology in modern markets such as mobile and edge computing, which is closely related to this subject.

The integration of SoC implies multiple benefits, the most notable ones being the reduced area usage, power consumption and latency, and increased performance than their multi-chip counterparts. As mentioned before, MPSoCs could gain popularity amongst engineers and researchers based on the success of Zynq.

## 6.2 Platform Overview

This section studies both the Zynq architecture and the PYNQ framework. Zynq UltraScale+ and PYNQ are very recent developments, in fact, PYNQ was only created a few years ago and while it has already proven itself really useful and grown a community, it still has a lot of growth potential.

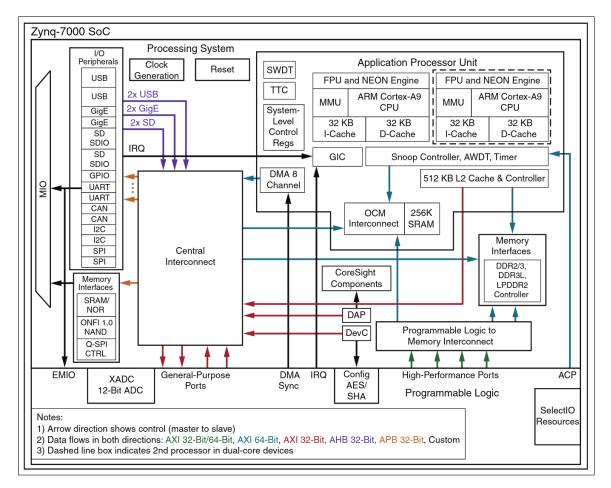

Fig. 6.1: Zynq-7000 architectural overview (source: [2])

#### 6.2.1 Zynq

This project uses Zynq UltraScale+ architecture [1], the successor to Zynq-7000. This document refers to Zynq as an inclusion of both, knowing that UltraScale+ is the most modern architecture. Zynq-7000 is a family of heterogeneous SoCs designed by Xilinx for complex tasks such as the machine vision studied in this project. It is designed with a processor-centric approach instead of the more traditional FPGA-centric approach. The processor-centric approach means the PS boots first and standard processes such as running the operating system or interacting with the board are done as in other, single processor devices. This makes the development process more natural to the majority of developers. This section analyzes the Zynq-7000 architecture and explicitly remarks differences with UltraScale when relevant.

Figure 6.1 shows the functional blocks and connections of functional blocks of the Zynq-7000 architecture. The processors are divided into the processing system or PS and the programmable logic or PL. The PS and PL communicate via AXI interfaces. AXI interfaces are designed for onchip communications and offer benefits for high-performance, parallel, synchronous communication. The bit size of the ports varies, some being of 32 bits, others of 64 and 128 bits. The AXI interfaces offer lower latency and higher bandwidth than more traditional connections. The AXI connections are seen in figure 6.1 as arrows between functional blocks. The legend of the figure gives additional information as to how to interpret the connections.

The PS can be seen in the upper half of figure 6.1 contains the application processor unit, memory interfaces, IO peripherals and the interconnect interface. Zynq 7000 devices have 32 bit ARM processors, while Zynq UltraScale+ devices have 64-bit processors. Zynq UltraScale+ devices also include a dual-core RPU and an optional GPU [3]. These paragraphs will examine each one of the main components in more detail. Each core of the processor in the APU has an L1 cache, there is an L2 cache that is shared between processors. It is worth noting that while the APU in figure 6.1 has two cores, the number of cores for Zynq UltraScale+ devices may be either two or four. It has low latency access to the on-chip RAM described later in this section. Although not explicitly discussed here, it also has standard features such as interruptions, timers, tracing mechanisms and a MMU to manage virtual memory.

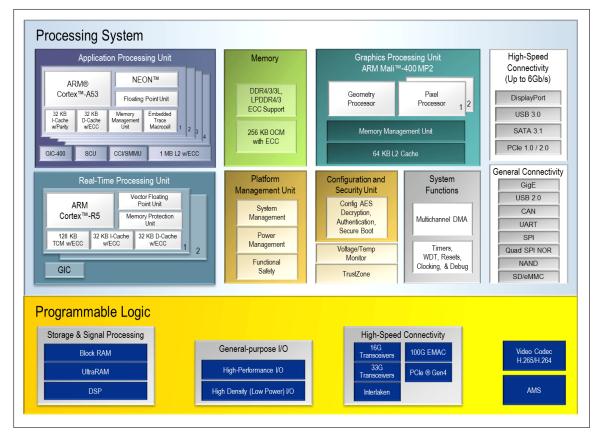

Fig. 6.2: Zynq-UltraScale+ component overview (source: [4])

The PS has two memory interface types: dynamic and static. The dynamic memory interfaces handle the CPU L2 caches, shared memory with the PL and interconnect components. They include a multi-protocol DDR memory controller that enables shared access to memory from both the PS and PL via AXI ports. The IO peripherals are explained in section 6.3, but it is worth noting that they can be exposed via multiplexed IO pins (MIO) or combining MIO and pins belonging to the PL. That combination is denominated extended MIO or EMIO. "Interconnect" refers to the connection between architectural components: APU, PL, IO peripherals and so on are connected to each other via multiplexed ARM AMBA AXI connections, again as shown in

Fig. 6.3: PL interface to PS memory (source: [4])

figure 6.1. According to the datasheets [4] the interconnect is designed in such a way that the most time-sensitive modules that require minimal latency have the shortest paths to memory. A QoS block exists to regulate traffic between the components. Figure 6.2 shows the components of the Zynq UltraScale+ architecture, which as already mentioned contains more features than the Zynq 7000 architecture.

Zynq UltraScale+ devices also include memory protection and peripheral protection units developed by Xilinx, additional units such as a platform management unit or a configuration and security unit, and a more advanced DMA controller. Lastly, more standard and high-speed peripheral connections are available than in Zynq-7000.

Regarding the PL, LUTs can be used either as a single 6 input 1 output LUT or as two 5 input 1 output LUTs. The equivalence is a 64 bit ROM for the single, 6 input LUT and two 32 bit ROMs for the dual 5 input LUTs. CLBs are composed of two slices that are themselves composed of four LUTs and corresponding components (e.g. two flip-flops corresponding to each LUT).

The PS-PL interface is complex and includes many components, protocols and ports. As seen in figures 6.1 and 6.3, communication from PL to PS happens when the PL writes to the four corresponding AXI ports. The writes are buffered with FIFO controllers. The output ports then go to either the DDR or OCM. This provides the PL a way of accessing the DDR and OCM memories of the PS, but when coherence is required in the access, the ACP interface should be used, shown in figure 6.1, which goes through the corresponding controllers.

Summing up, Zynq is an architecture that offers a PS-centric approach and a low-consumption, low-latency, highly efficient connection between the PS and PL.

Fig. 6.4: PYNQ application overview (source [5])

## 6.2.2 PYNQ

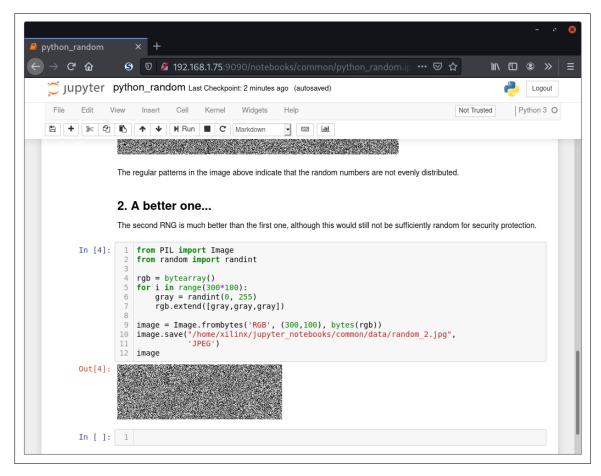

PYNQ is an open-source framework that enables development for the Zynq architecture without requiring the design of PL circuits. Software for PYNQ is developed in Python. The framework has Jupyter Notebooks installed so academical or explanatory documents containing executable, live code can be created. This is useful not only for getting used to the framework while going through the notebooks but also to develop in an organized way and to publish the research results in an accessible manner. Multiple introductory notebooks are included in PYNQ to get familiarized with the framework. An overview of PYNQ is shown in figure 6.4. The framework includes a Python library, documentation, programs that serve as examples, amongst others.

PYNQ is also the name of the Python library. The library setup scripts contain functions to validate the device it is installed on and to install additional utilities such as the documentation or the introductory Jupyter Notebooks. PYNQ can be downloaded from prebuilt binaries or manually compiled from an appropriate version of the repository in a supported device.

The library exposes many functionalities of Zynq, such as IO operations, PS/PL management or memory management. It provides acceleration abstraction using overlays. A PYNQ overlay is a hardware library or PL design that allows the implementation of applications to the PL in addition of the PS. An API for controlling the overlays and thus the PL from Python is offered in the PYNQ library. The accelerated part of an application is located in an overlay. Designs can be downloaded to the PL without overlays by using bitstreams. Overlays include both a bitstream (.bit) and scripting (.tcl) files that usually enables, amongst other things, to identify Zynq system configurations or to rebuild the Vivado project from the overlay. Both overlays and bitstreams have corresponding Python classes in the library. Additionally, PYNQ is reliant on NumPy [6] for data management and is compatible with Asyncio [7]. As explained in section 6.2.2.2, NumPy is a scientific computing library and Asyncio offers a high level concurrency model, both very useful for PYNQ enabled devices.

PYNQ is pushing boundaries, allowing developers without expertise on programmable logic to develop programs that run on FPGAs with the considerable performance benefits it implies.

#### 6.2.2.1 PYNQ application example

The PYNQ Hello World repository [8] created by Xilinx provides a good example to visualize how PYNQ allows exploiting the benefits offered by Zynq without diving too deep into architecture specifics. The example shows only the most relevant segments, but the full example can be accessed at the source. In this specific example, the PL will be used to scale an image from dimensions AxB to dimensions CxD. This is done with an IP of the resizer.bit overlay. Listing 6.1 shows the overlay download and the assignation of the DMA, resizer IP and memory allocator to Python variables.

```

1 resize_design = Overlay("resizer.bit")

2 dma = resize_design.axi_dma_0

3 resizer = resize_design.resize_accel_0

4 xlnk = Xlnk()

```

Listing 6.1: "IP extraction from the resizer overlay"

After opening an image and saving it in a variable called image, the values forming the image exist only in the local memory of Python. By allocating shared memory with Xlink, the developer is able to save and read data from addresses that will also be accessible to the PL thanks to the DMA. This is done with the code shown in listing 6.2. The image will be resized from AxB to CxD, each with three 8-bit color channels, thus the shape of the array.

```

1 in_buffer = xlnk.cma_array(shape=(A, B, 3), dtype=np.uint8, cacheable=1)

2 out_buffer = xlnk.cma_array(shape=(C, D, 3), dtype=np.uint8, cacheable=1)

3 in_buffer[:] = np.array(image)

```

Listing 6.2: "Memory allocation"

The last statement makes a deep copy of the image that was on the local Python memory to the shared memory. It is necessary to make a deep copy, as by default Python uses references when copying lists and other objects. Figure 6.5 shows an scheme of Zynq at this point of execution.

Fig. 6.5: State of the program with image in local and shared memory (source [8])

The next step is to make the data accessible to the PL, wait for it to process it, and read the results. Listing 6.3 writes the old and new dimensions to the corresponding registers (0x10 for A, 0x18 for B and so on), associates the shared memory previously allocated with the PL, starts the process by writing to the corresponding segment (0x81) and waits for the result to be written to the memory address associated to the output.

```

resizer.write(0x10, A)

1

\mathbf{2}

resizer.write(0x18, B)

3

resizer.write(0x20, C)

resizer.write(0x28, D)

4

5

6

dma.sendchannel.transfer(in_buffer)

7

dma.recvchannel.transfer(out buffer)

8

resizer.write(0x00,0x81)

9

dma.sendchannel.wait()

10 dma.recvchannel.wait()

```

```

Listing 6.3: "PL usage"

```

It should be mentioned that theses steps can easily be abstracted from the end user by providing higher-level functions that handle specific addresses, thus in some PYNQ applications it will be managed by the library itself instead of the library user. Figure 6.6 shows the components involved in the data being processed by the PL.